台积电表示2nm工艺将于2025年末进入量产 将使用GAA技术

- 来源:超能网

- 作者:吕嘉俭

- 编辑:豆角

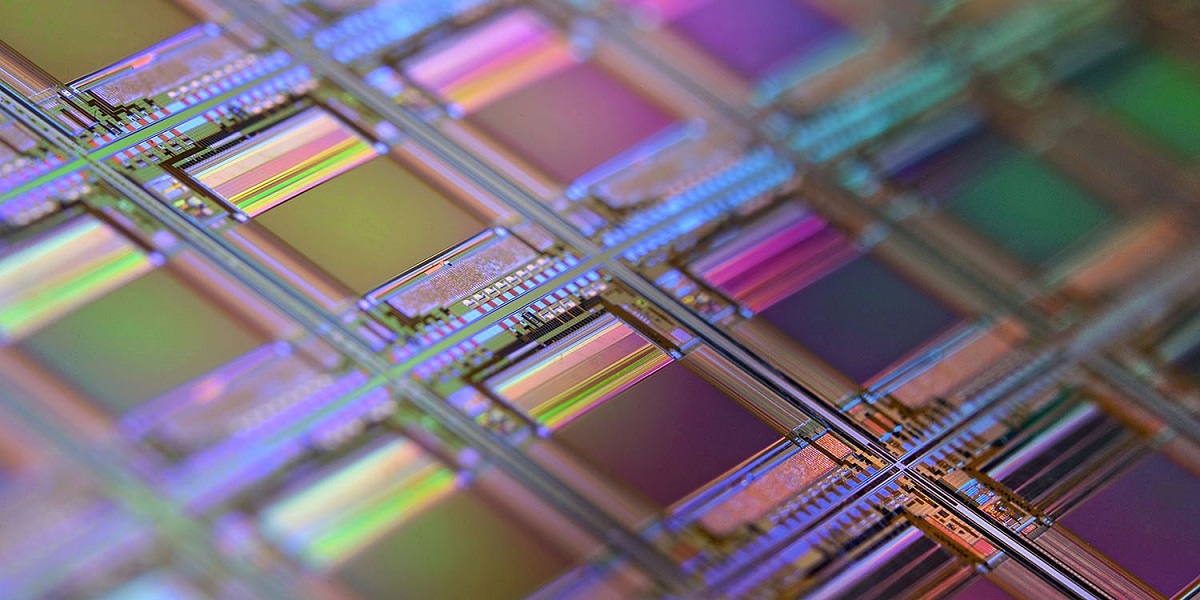

近期传出台积电(TSMC)在3nm工艺开发上取得突破,第二版3nm制程的N3B会在今年8月份率先投片,第三版3nm制程的N3E的量产时间可能由原来的2023年下半年提前到2023年第二季度。去年台积电总裁魏哲家曾表示,N3制程节点仍使用FinFET晶体管的结构,推出的时候将成为业界最先进的PPA和晶体管技术,同时也会是台积电另一个大规模量产且持久的制程节点。

在实现3nm工艺上的突破后,台积电似乎对2nm工艺变得更加有信心。据TomsHardware报道,本周台积电总裁魏哲家证实,N2制程节点将如预期那样使用Gate-all-around FETs(GAAFET)晶体管,,制造的过程仍依赖于现有的极紫外(EUV)光刻技术。预计台积电在2024年末将做好风险生产的准备,并在2025年末进入大批量生产,客户在2026年就能收到首批2nm芯片。

魏哲家认为,台积电N2制程节点在研发上已走上正轨,无论晶体管结构和工艺进度都达到了预期。

随着晶体管变得越来越细小,台积电采用新工艺技术上的速度也变慢了,以往大概每两年就会进入一个新的制程节点,现在则要等更长的时间。N2制程节点的时间表一直都不太确定,台积电在2020年首次确认了该项工艺的研发,根据过往信息,2022年初开始建设配套的晶圆厂,预计2023年中期完成建筑框架,2024年下半年安装生产设备。

玩家点评 (0人参与,0条评论)

热门评论

全部评论